| Indeks | English version |

Starsza wersja mikrokomputera MK-85 była zbudowana z następujących układów scalonych:

W nowszej, bardziej rozpowszechnionej wersji, mikroprocesor i sterownik wejścia/wyjścia znalazły się na jednym chipie a dwie pamięci ROM o pojemności 8kB zostały zastąpione jedną o pojemności 16kB. Lista układów scalonych:

Przedstawione tu informacje dotyczą tej nowszej wersji.

Informacja, gdzie można znaleźć schemat jest podana na stronie odnośników.

| Adres | Rozmiar danej | Funkcja |

|---|---|---|

| $80-$FF | bajt | Port szeregowy sterownika wyświetlacza ciekłokrystalicznego |

| $100 | słowo | Rejestr danych równoległego portu wejsciowego KB, bity 8-2 używane jako wejścia kolumn matrycy klawiatury |

| $102 | słowo | Rejestr danych równoległego portu dwukierunkowego PP, bity 3-1 używane jako wyjścia wierszy matrycy klawiatury |

| $104 | słowo | Rejestr sterujący/stanu |

Sterownik wyświetlacza stosowany w starszej wersji mikrokomputera Elektronika MK-85 nie ma własnej pamięci i korzysta z systemowej pamięci RAM. W procedurę wyświetlania jest również zaangażowany sterownik wejścia/wyjścia. Co 0.4 ms przerywa on wykonywanie programu przez procesor i za pomocą DMA przesyła wybrany fragment pamięci RAM do sterownika wyświetlacza.

Nowsza wersja sterownika wyświetlacza ma wbudowaną pamięć RAM i w związku z tym wymaga obsługi tylko wtedy, gdy nastąpiła zmiana wyświetlanej informacji. Nie ma już potrzeby bezpośredniego dostępu do pamięci (DMA).

Łączność ze sterownikiem wyświetlacza odbywa się przez szeregową magistralę. Wysyłanie danych następuje przez zapis pod adres z przedziału $0080-$00FF. Ważne jest tylko 5 mniej znaczących bitów danej.

| Końcówka | Nazwa | Funkcja |

|---|---|---|

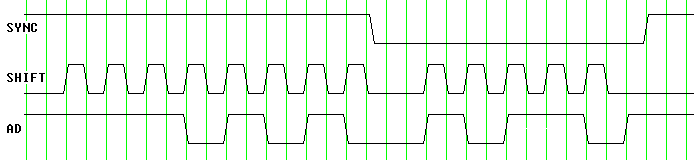

| 2 | SYNC | Poziom wysoki przy przesyłaniu adresu, niski przy przesyłaniu danych. |

| 62 | SHIFT | Impulsy zegarowe dla rejestru przesuwającego. |

| 1 | AD | Przesyłane dane, najpierw bit najmniej znaczący, jako zero logiczne przyjęty został wysoki poziom, jako jedynka logiczna niski poziom. |

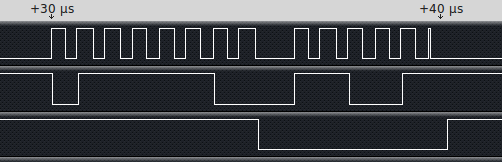

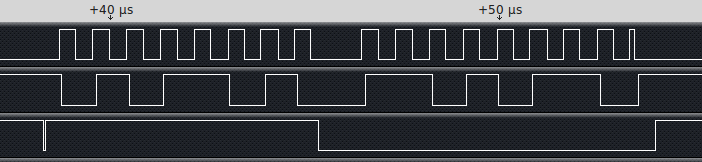

Na poniższym wykresie przesyłana jest przykładowa dana $12 pod adres $00A8.

Na wykresie z analizatora logicznego widać dodatkowy krótki impuls SHIFT o szerokości ok. 0.1 µs.

Późniejsze wersje mikroprocesora Т36ВМ1-2 wysyłają 8 bitów danych zamiast 5. Zmiana nastąpiła gdzieś pomiędzy datami produkcji 9105 do 9109.

Z przeprowadzonych testów wynika, że sterownik wyświetlacza bierze pod uwagę tylko pierwszych 5 odebranych bitów danych. Wszystkie następne są ignorowane.

| Adres | Funkcja |

|---|---|

| $80-$DF | Ten przedział adresów wybiera wewnętrzną pamięć RAM sterownika LCD. |

| $E0 | Ten rejestr określa pozycję i kształt sprzętowo generowanego kursora. bity 3-0 definiują pozycję kursora (wartość $0C gdy kursor nie ma być wyświetlany) bit 4 definiuje kształt kursora, wypełniony prostokąt gdy bit skasowany, podkreślenie gdy bit ustawiony |

| $E8 | Funkcja niewiadoma, wartość inicjowana na 0 |

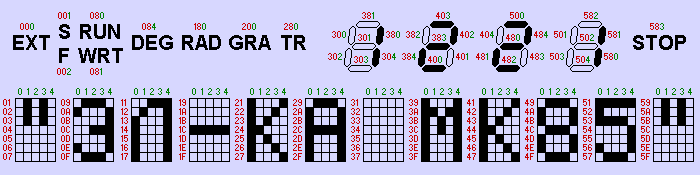

Rysunek przedstawia przyporządkowanie pikseli wyświetlacza ciekłokrystalicznego do adresów w pamięci RAM.

Liczby w kolorze czerwonym reprezentują ofsety adresów licząc od początku pamięci wyświetlacza.

Liczby w kolorze zielonym reprezentują numer bitu w bajcie.

Interfejs klawiatury składa się z dwóch 16-bitowych portów:

Matryca klawiatury jest skanowana przez wpisywanie logicznych jedynek do kolejnych bitów portu wybierającego wiersze, a następnie odczyt portu kolumn. Wciśnięcie klawisza powoduje połączenie wiersza z dwoma kolumnami za pomocą podwójnych styków.

Interfejs klawiatury ma możliwość obudzenia procesora ze stanu bezczynności, gdy któryś bit portu kolumn zmieni stan z 0 na 1.

Jednoczesne pojawienie się niskiego poziomu na wejściach KB9 i KB10 (końcówki 10 i 11) lub na wejściach KB0 i KB10 (końcówki 1 i 11) wyzwala przerwanie HALT.

W mikrokomuterze Elektronika MK-85 wejścia KB9/KB10 odczytują stan klawisza STOP wybieranego wyjściem PP1.

Wciśnięcie tego klawisza powoduje zgłoszenie przerwania HALT, którego wektor procedury obsługi znajduje się pod adresem $0078.

Gdy bit priorytetu przerwania I (bit 7) w rejestrze PSW jest skasowany, to pojawienie się niskiego poziomu na porcie PP1 (końcówka 15), niezależnie od tego czy jest skonfigurowany jako wejście lub wyjście, powoduje zgłoszenie przerwania EVNT. Wektor procedury obsługi tego przerwania znajduje się pod adresem $0040 (nie używane w MK-85).

Jednoczesne pojawienie się niskiego poziomu na wejściach KB0 i KB1 (końcówki 1 i 2) wprowadza procesor w stan wyłączonego zasilania.

Stan ten jest zachowywany przy podaniu niskich poziomów na wejścia KB9 i KB10 (końcówki 10 i 11) lub wejścia KB0 i KB10 (końcówki 1 i 11).

Zmiana poziomu chociaż jednego z tych wejść na wysoki powoduje reset mikroprocesora.

Powtórna zmiana poziomu wejść KB0/KB10 lub KB9/KB10 na niski wyzwala przerwanie HALT.

System może być zatem wyłączany za pomocą pary styków wymuszających niski poziom na wejściach KB0/KB1, oraz włączany za pomocą pary styków wymuszających niski poziom na wejściach KB0/KB10 lub KB9/KB10.

Wybór zależy od rozmiaru zastosowanej pamięci ROM (8kB lub 32kB).

| Bit (dzies.) | Funkcja |

|---|---|

| 0 | Ten bit wybiera kierunek grupy końcówek PP3-PP1 portu dwukierunkowego (wejścia gdy bit ustawiony). W mikrokomputerze Elektronika MK-85 sterują one wierszami matrycy klawiatury, są zatem skonfigurowane jako wyjścia. |

| 1 | Ten bit wybiera kierunek grupy końcówek PP7-PP4 portu dwukierunkowego (wejścia gdy bit ustawiony). |

| 2 | Ten bit wybiera kierunek grupy końcówek PP11-PP8 portu dwukierunkowego (wejścia gdy bit ustawiony). |

| 3 | Ten bit wybiera kierunek grupy końcówek PP15-PP12 portu dwukierunkowego (wejścia gdy bit ustawiony). W mikrokomputerze Elektronika MK-85 przełączają one stałą czasową obwodu RC generatora częstotliwości zegarowej. Ustawienie tego bitu przyspiesza pracę procesora. |

| 4 | Ten bit jest ustawiany, gdy na końcówce PP1 zostanie wykryty niski poziom trwający conajmniej 20ns. Może być skasowany tylko przez zapis do rejestru. |

| 5-9 | Te bity wybierają konfigurację zewnętrznej pamięci (wielkość pamięci ROM i RAM). |

| 10 | Skasowanie tego bitu zatrzymuje zegar procesora. |

| 11 | Skasowanie tego bitu dzieli częstotliwość zegara procesora przez 8. Program w pamięci ROM mikrokomputera Elektronika MK-85 obsługuje w tym trybie klawiaturę i generację opóźnień. |

| 12 | Ustawienie tego bitu wyłącza zasilanie procesora. |

Przy przejściu w tryb HALT procesor zapisuje poprzednie wartości PC i PSW w specjalnych wewnętrznych rejestrach procesora CPC i CPS (dostępnych w trybie HALT za pomocą instrukcji RCPC/RCPS i WCPC/WCPS), a następnie następuje przekazanie sterowania do procedury obsługi przerwania HALT poprzez wektor pod adresem utworzonym z bardziej znaczącego bajtu rejestru SEL oraz stałej wartości $78 w mniej znaczącym bajcie.

| Instrukcja | Opcode | Funkcja | Opis |

|---|---|---|---|

| GO | $000A | PC <- CPC PSW <- CPS |

powrót do USER mode |

| STEP | $000E | PC <- CPC PSW <- CPS |

tak jak GO, z wyjątkiem zablokowania przerwań HALT na czas wykonywania następnej instrukcji, używana do pracy krokowej programu |

| RSEL | $0010 | R0 <- SEL | odczyt rejestru SEL, w przypadku MK-85 zwraca $0000 |

| MFUS | $0011 | R0 <- (R5)+ | odczyt z obszaru adresowego USER |

| RCPC | $0012 | R0 <- CPC | odczyt rejestru CPC |

| RCPS | $0014 | R0 <- CPS | odczyt rejestru CPS |

| MTUS | $0019 | -(R5) <- R0 | zapis do obszaru adresowego USER |

| WCPC | $001A | CPC <- R0 | zapis rejestru CPC |

| WCPS | $001C | CPS <- R0 | zapis rejestru CPS |

Przy zbieraniu powyższych informacji bardzo mi pomógł Vladimir Poletaev, dziękuję!