| Indeks | English version |

Nazwy sygnałów na podstawie książki "PB-1000 technical handbook" wydanej przez MODERN CO, LTD, Japan.

Podziękowania dla BLUE za ogromną pomoc.

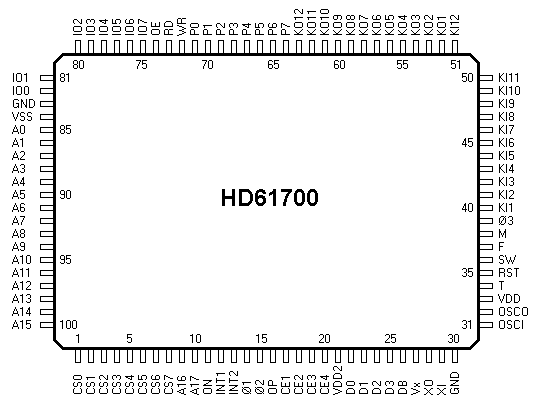

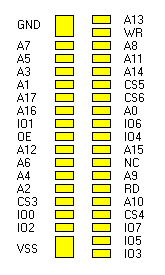

| Końcówka | Symbol | Funkcja |

|---|---|---|

| 1..8 | CS0..CS7 | Chip Select, aktywny niski poziom.

Poszczególne wyjścia dekodują następujące zakresy adresów: CS0: &H08000..&H0FFFF, ROM 32kB CS1: &H04000..&H05FFF, idzie do złącza dodatkowych urządzeń, funkcja nieznana CS2: &H06000..&H07FFF, wewnętrzna pamięć RAM 8kB CS3: &H18000..&H19FFF, moduł rozszerzenia pamięci RAM CS4: &H1A000..&H1BFFF, moduł rozszerzenia pamięci RAM CS5: &H1C000..&H1DFFF, moduł rozszerzenia pamięci RAM CS6: &H1E000..&H1FFFF, moduł rozszerzenia pamięci RAM CS7: &H00C00..&H00C0F, interfejs portu szeregowego, drukarki i stacji dysków elastycznych |

| 9,10 | A16,A17 | dwa najbardzej znaczące bity szyny adresowej |

| 11 | ON | wejście zewnętrznych przerwań ON Interrupt, dostaje impulsy o częstotliwości 55 Hz z końcówki 27 układu sterownika wyświetlacza HD44352, używa adresu procedury obsługi &HFFCA |

| 12 | INT1 | wejście zewnętrznych przerwań wyzwalane zboczem, wyprowadzone do złącza dodatkowych urządzeń, używa adresu procedury obsługi &HFFBB |

| 13 | INT2 | wejście zewnętrznych przerwań wyzwalane poziomem, wyprowadzone do złącza dodatkowych urządzeń, używa adresu procedury obsługi &HFFD0 |

| 14..25 | Ø1,Ø2 OP CE1..CE4 VDD2 D0..D3 |

magistrala sterownika wyświetlacza, podobna jak w Casio FX-700P, zanegowana logika wszystkich sygnałów, wyjścia CE3 i CE4 nie są wykorzystane w Casio PB-1000 |

| 26 | DB | zworka E do VSS (rozwarta), niski poziom wybiera tryb debug |

| 27 | Vx | kondensator elektrolityczny 0.47uF filtrujacy napięcie zasilające oscylatora 32768Hz |

| 28,29 | XO,XI | kwarc 32768Hz, XO jest wyjściem inwertera oscylatora |

| 30 | GND | połączona do GND |

| 31,32 | OSCI,OSCO | rezonator ceramiczny 910kHz, OSCO jest wyjściem inwertera oscylatora |

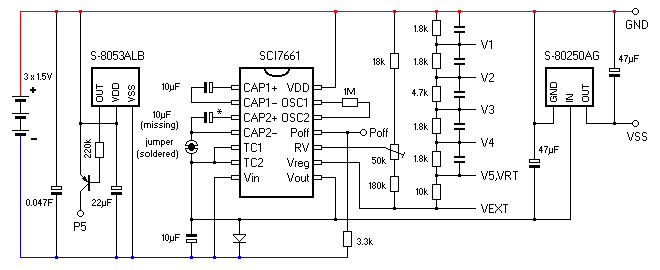

| 33 | VDD | wyjście zasilania, niski poziom gdy kalkulator jest włączony, steruje wejściem Poff układu scalonego przetwornicy napięcia SCI7661 (poprzez inwerter na tranzystorze pnp) |

| 34 | T | może być podłączona do GND przez zworkę A (zalutowana) albo do VSS przez zworkę C (rozwarta), niski poziom wybiera tryb testowy |

| 35 | RST | wejście Reset, aktywny niski poziom, wciśnięcie styku RESET zwiera tą końcówkę do VSS |

| 36 | SW | wejście zgłoszenia przerwania od włączenia zasilania, łączone przez wyłącznik zasilania do VSS (włączone) albo do GND (wyłączone), używa adresu procedury obsługi &HFFC1 |

| 37 | F | wyjście informujące czy częstotliwość oscylatora jest dzielona przez 16 wysoki poziom: wolniejsza praca procesora, niski poziom: szybsza praca procesora (przeciwnie do opisu w "technical handbook") |

| 38 | M | sygnał pobierania kodu rozkazu w trybie debug |

| 39 | Ø3 | sygnał odczytu z szyny danych w trybie debug |

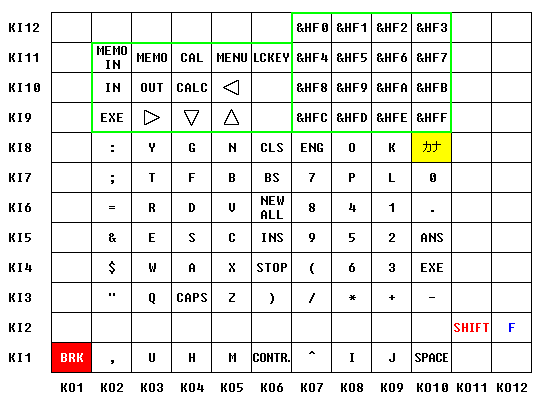

| 40..51 | KI1..KI12 | port wejściowy matrycy klawiatury, dostępny przez rejestr KY wejście KI5 może być opcjonalnie zwarte do VSS za pomocą zworki B, przeznaczenie nieznane |

| 52..63 | KO1..KO12 | port wyjściowy matrycy klawiatury, sterowany przez rejestr IA |

| 64..71 | P7..P0 | 8-bitowy dwukierunkowy port dostępny przez rejestry PD i PE.

Funkcja poszczególnych bitów portu: P7,P6 sterują głośniczkiem piezoelektrycznym P5 odczytuje stan napięcia zasilającego P4 jest wyjściem reset dla urządzeń peryferyjnych P3 załącza zasilanie interfejsu FDD, 0 gdy włączone P2 wybiera kierunek transferu FDD, 1 gdy zapis do interfejsu FDD, 0 gdy odczyt z interfejsu FDD P1 jest wyprowadzony na złącze, ale nie używany P0 jest wejściem sygnału potwierdzenia wyboru kierunku transmisji interfejsu FDD |

| 72 | WR | sygnał strobu zapisu, aktywny niski poziom |

| 73 | RD | sygnał strobu odczytu, aktywny niski poziom |

| 74 | OE | sygnalizuje ważne dane, wygląda jak sygnał sterujący E występujący w magistrali firmy Motorola, nie używany w PB-1000 (chyba, że przez jakieś zewnętrzne urządzenia) |

| 75..82 | IO7..IO0 | dwukierunkowa szyna danych |

| 83 | GND | plus zasilania |

| 84 | VSS | minus zasilania |

| 85..100 | A0..A15 | szyna adresowa |

Wykres ilustruje przebiegi na magistrali systemowej i na porcie LCD zarejestrowane w czasie wykonywania następującego programu:

8E35: 54 00 C3 PPO &HC3

8E38: 52 0D STL &H0D ;dana &H0D jest przesyłana w dwóch cyklach,

;najpierw cyfra mniej znacząca

8E3A: 27 00 PHU $0 ;zapis danej &H7A pod adres &H6A2F

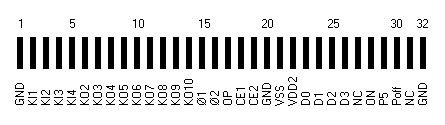

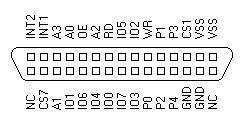

Kolumny matrycy klawiatury są wybierane przez 12-bitowy port wyjściowy KO, sterowany za pomocą rejestru IA. Wciśnięty klawisz łączy wybraną kolumnę z jednym z wierszy. Linie wierszy są odczytywane przez 12-bitowy port wejściowy KI, dostępny poprzez rejestr KY.

Relacja pomiędzy bitami rejestru KY a wierszami klawiatury:

![]()

Autorem grafik jest Mahmoud Yassine.